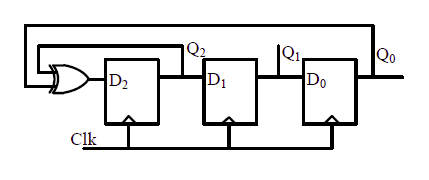

The propagation delay of the exclusive$-\text{OR}$ ($\text{XOR}$) gate in the circuit in the figure is $3\:ns$. The propagation delay of all the flip-flops is assumed to be zero. The clock ($\text{Clk}$) frequency provided to the circuit is $500\: \text{MHz}$.

Starting from the initial value of the flip-flop outputs $Q_{2}Q_{1}Q_{0} = 1\;1\;1$ with $D_{2}=1$, the minimum number of triggering clock edges after which the flip-flop outputs $Q_{2}Q_{1}Q_{0}$ becomes $1\; 0\; 0$ (in integer) is