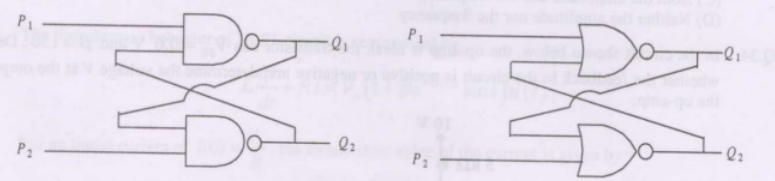

Refer to the NAND and NOR latches shown in the figure. The inputs $\left(P_{1}, P_{2}\right)$ for both the latches are first made $(0,1)$ and then, after a few seconds, made $(1,1)$. The corresponding stable outputs $\left(Q_{1}, Q_{2}\right)$ are

- NAND: first $(0,1)$ then $(0,1)$ NOR: first $(1,0)$ then $(0,0)$

- NAND: first $(1,0)$ then $(1,0)$ NOR: first $(1,0)$ then $(1,0)$

- NAND: first $(1,0)$ then $(1,0)$ NOR: first $(1,0)$ then $(0,0)$

- NAND: first $(1,0)$ then $(1,1)$ NOR: first $(0,1)$ then $(0,1)$