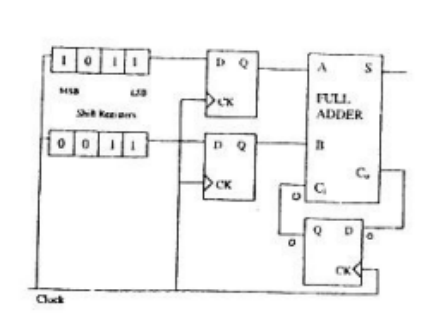

For the circuit shown in figure below, two $4$-bit parallel-in serial-out shift registers loaded with the data shown are used to feed the data to a full adder. Initially, all the flip-flops are in clear state. After applying two clock pulses, the outputs of the fulladder should be

- $\mathrm{S}=0, \mathrm{C}_{0}=0$

- $\mathrm{S}=0, \mathrm{C}_{0}=1$

- $\mathrm{S}=1, \mathrm{C}_{0}=0$

- $\mathrm{S}=1, \mathrm{C}_{0}=1$