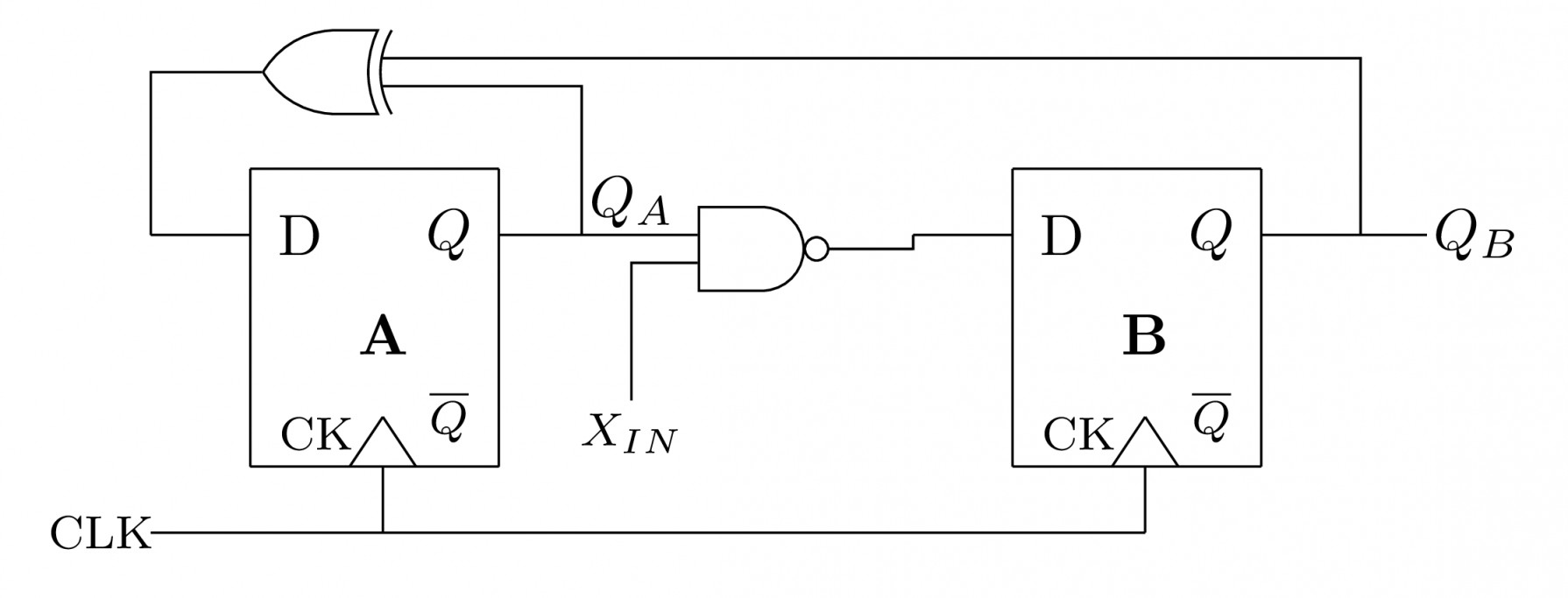

A finite state machine (FSM) is implemented using the D flip-flop A and B, and logic gates, as shown in the figure below. The four possible states of the FSM are $Q_{A}Q_{B}=00,01,10$ and $11$.

Assume that $X_{IN}$ is held at a constant logic level throughout the operation of the FSM. When the FSM is initialized to the state $Q_{A}Q_{B}=00$ and clocked, after a few clock cycles, it starts cycling through

- all of the four possible states if $X_{IN}=1$

- three of the four possible states if $X_{IN}=0$

- only two or four possible states if $X_{IN}=1$

- only two or four possible states if $X_{IN}=0$