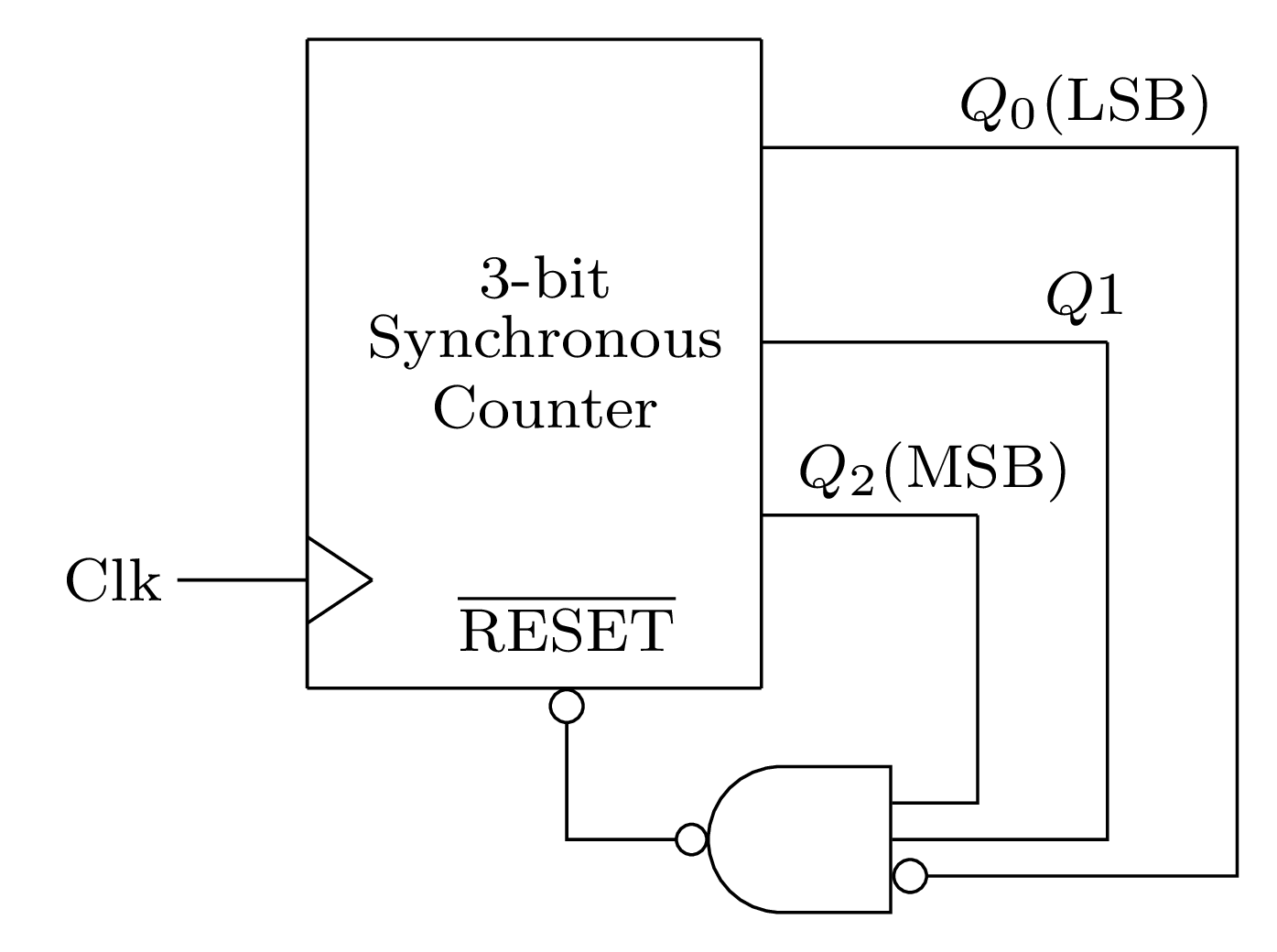

For the circuit shown in the figure, the delay of the bubbled NAND gate is $2\:ns$ and that of the counter is assumed to be zero.

If the clock (Clk) frequency is $1\:GHz$, then the counter behaves as a

- $\text{mod}-5\:\text{counter}$

- $\text{mod}-6\:\text{counter}$

- $\text{mod}-7\:\text{counter}$

- $\text{mod}-8\:\text{counter}$