In this question Nand gate delays not mentioned, so I am assuming 2 Nand gates have unequal delays.

According to Latch functionality, the output of which gate is faster (i.e less delay) will affect the output of slower gate (i.e more delay).

So we are taking two different delays and observing the output sequences:

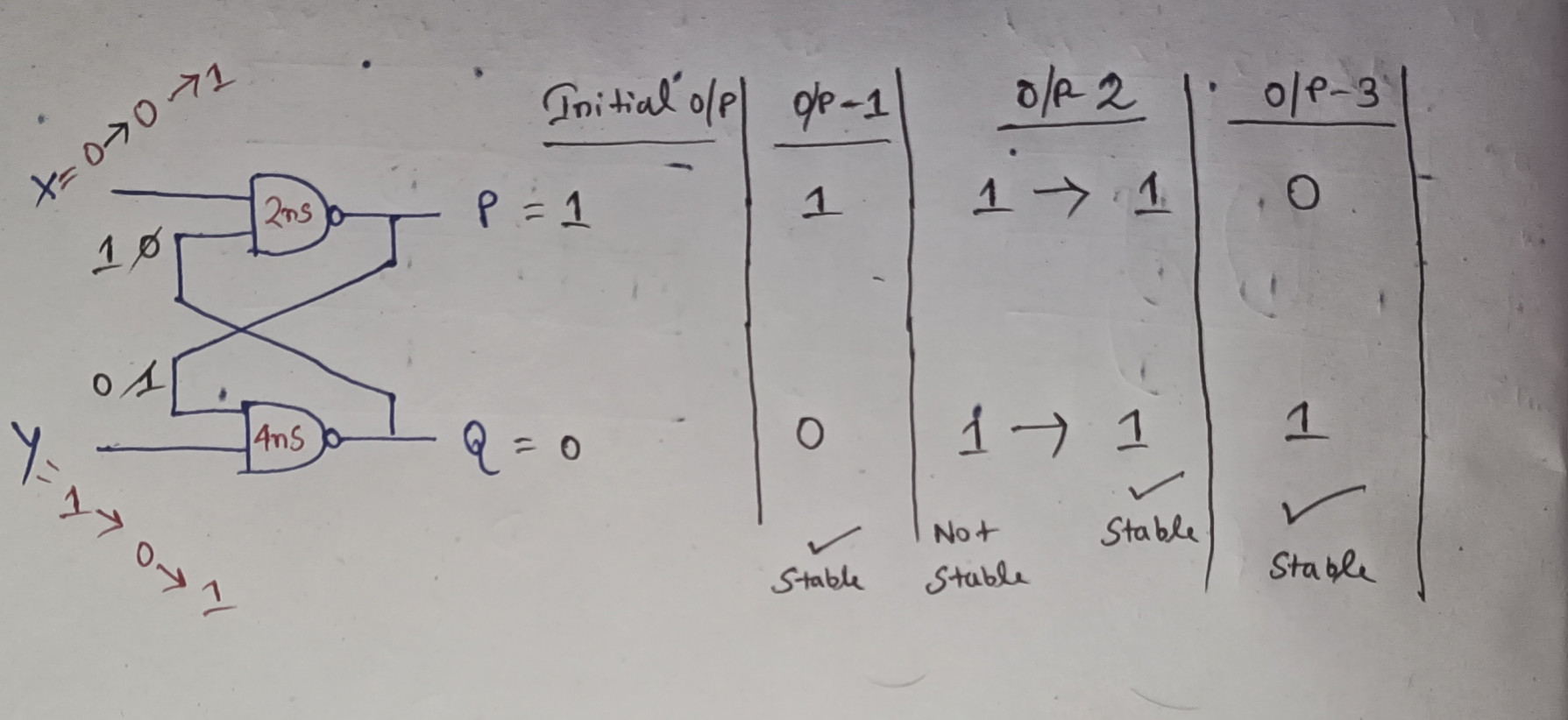

Case 1:

Upper NAND gate is faster (i.e less delay) and whenever it gives output, i.e P, that output will immediately go to the input side of belwo Nand gate and then we will get the output from below gate i.e Q

So we are applying the input sequence

XY = 01 --> 00 --> 11

And we got the output sequence as :

PQ = 10 --> 11 --> 01

The output sequence is shown below:

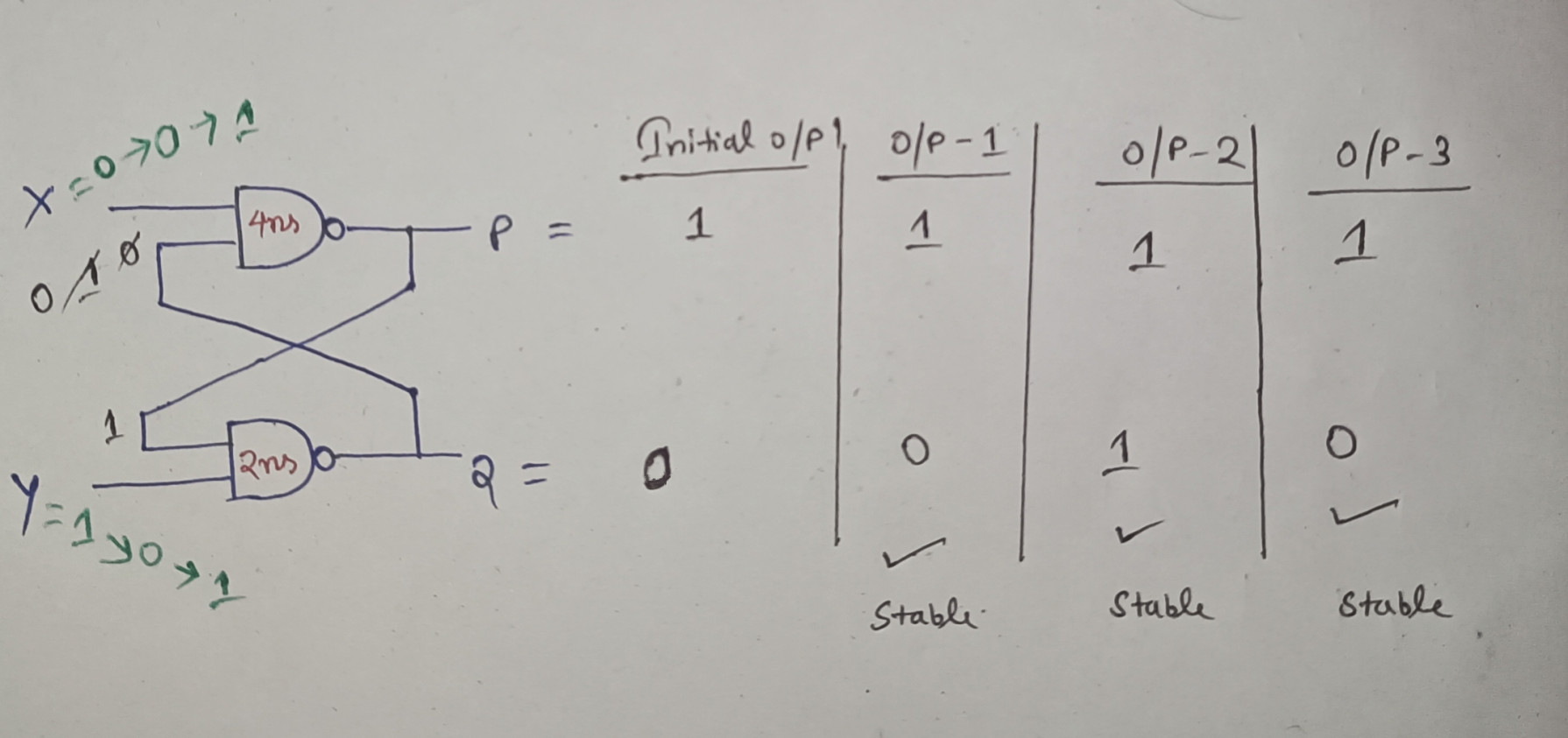

Case 2:

Now we are taking upper NAND gate is slower and lower NAND gate is faster. So lower one i.e output Q will generate first and then it will go to the input side of upper Nand gate and we will get the output P.

So we are applying the input sequence

XY = 01 --> 00 --> 11

And we got the output sequence as :

PQ = 10 --> 11 --> 10

So option C is correct.