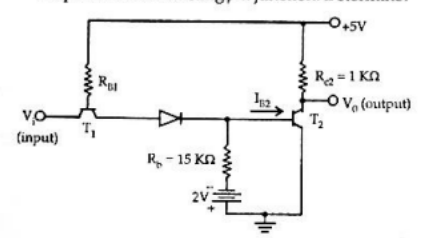

Each transistor in the figure is has dc current gain $\beta_{dc}=50$, cut-in voltage $V_{\gamma}=0.65 \mathrm{~V}$ and $\mathrm{V}_{\mathrm{BE’} \text { sat}}=0.75 \mathrm{~V}$. The output voltage $\mathrm{V}_{0}$ for $\mathrm{T}_{2}$ in saturation can be as high as $0.2 \mathrm{~V}$. Assume $0.7 \mathrm{~V}$ drop across a conducting $p-n$ junction. Determine?

- the minimum value $\mathrm{I}_{\mathrm{B} 2}$ necessary to keep $\mathrm{T}_{2}$ saturation.

- the maximum permissible value for the resistance $R_{\mathrm{BJ}}$.

- the worst-case high input (logic $1$) and the worst-case low input (logic 0) for which $\mathrm{T}_{2}$ will be either in saturation or in cut-off.