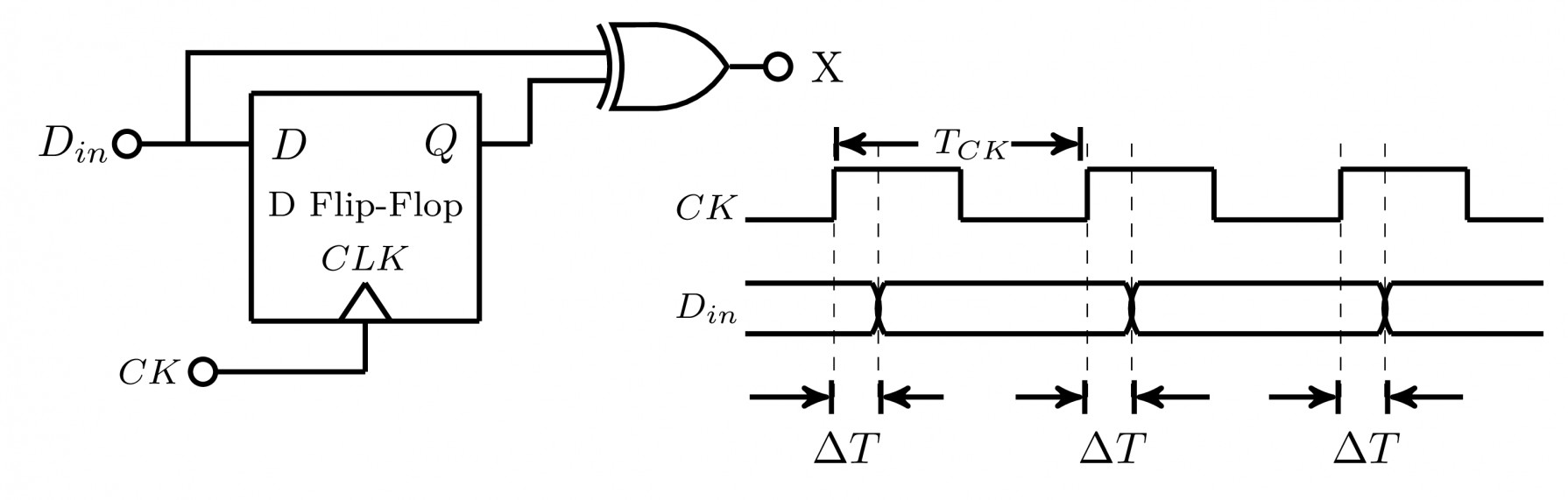

In the circuit shown below, a positive edge-triggered $D$ Flip-Flop is used for sampling input data $D_{in}$ using clock $CK$. The XOR gate output $3.3$ volts for logic HIGH and $0$ volts for logic LOW levels. The data bit and clock periods are equal and the value of $\Delta T/T_{CK}=0.15,$ where the parameters $\Delta T$ and $T_{CK}$ are shown in the figure. Assume that the Flip-Flop and the XOR gate are ideal.

If the probability of input data bit $\left ( D_{in} \right )$ transition in each clock period is $0.3$, the average value (in volts, accurate to two decimal places) of the voltage at node $X$, is _________.