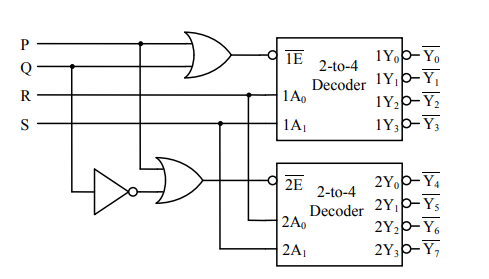

A $1$-to-$8$ demultiplexer with data input $D_{in}$ , address inputs $S_{0}, S_{1}, S_{2}$ (with $S_{0}$ as the LSB) and $\overline{Y_{0}}$ to $\overline{Y_{7}}$ as the eight demultiplexed outputs, is to be designed using two $2$-to-$4$ decoders (with enable input $\overline{E}$ and address inputs $A_{0}$ and $A_{1}$) as shown in the figure. $D_{in} , S_{0}, S_{1}$ and $S_{2}$ are to be connected to $P, Q, R$ and $S,$ but not necessarily in this order. The respective input connections to $P, Q, R,$ and $S$ terminals should be

- $S_{2}, D_{in}, S_{0}, S_{1}$

- $S_{1}, D_{in}, S_{0}, S_{2} $

- $D_{in}, S_{0}, S_{1}, S_{2} $

- $D_{in}, S_{2}, S_{0}, S_{1}$